# Welcome to Part 2 of the Altium Designer Workshop!

#### **Workshop Overview**

#### **√**Part 1: Schematic Design

- ✓ Basics of Altium Designer

- ✓ Adding components

- ✓ Connecting components

- ✓ Bonus Material: Hierarchical Schematics

#### Part 2: PCB Design

- Moving from schematic to PCB layout

- Layout tips and best practices

- Routing techniques

- Silkscreen tips

- Bonus Material: Multilayer PCBs

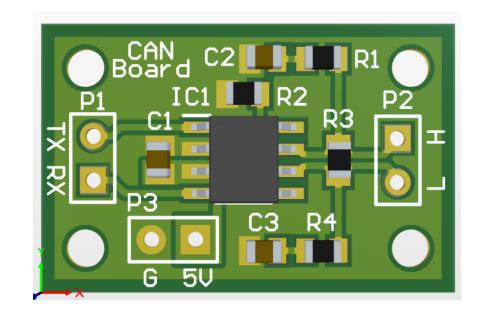

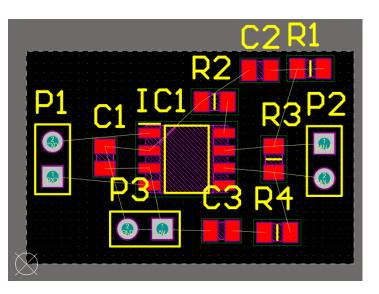

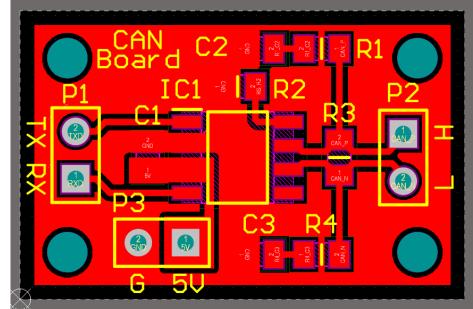

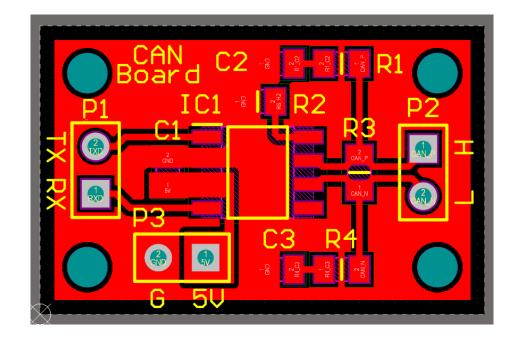

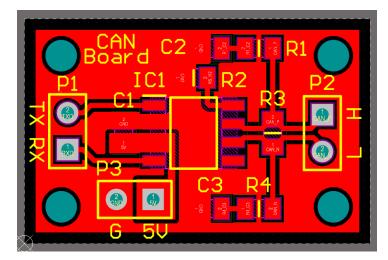

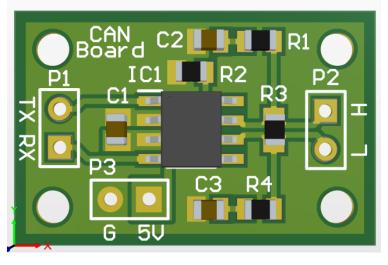

- Final Deliverable: 2-layer CAN transceiver PCB design

#### **Getting Started!**

#### <u>Tasks:</u>

- https://tinyurl.com/AltiumFall2022

- Make a new PCB file (and save it!)

- Set origin to bottom left corner

- Edit board shape/size (940 mil x 610 mil)

- Remember to be in Board Planning Mode (1 on your keyboard)

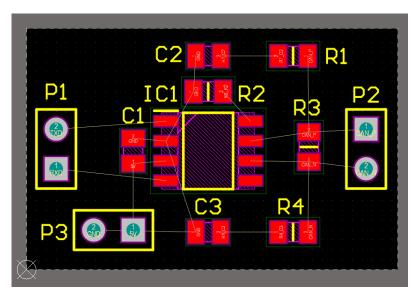

## **Beginning Your Layout**

#### <u>Tasks:</u>

- Import changes from schematic to PCB

- Do an initial layout (rough draft!)

#### Shortcuts:

- 1 = Board Planning Mode

- 2 = 2D Mode

- 3 = 3D Mode

- Ctrl + Scroll = Zoom

- Right Click + Drag = Move schematic/PCB

- Click and Hold + Space = Rotate component

- Backspace = Undo Net/Trace Segment

- Esc = Exit active tool

- Right click + drag from right to left = select entire object from part of it

- Right click + drag from left to right = select object that is completely covered

- Clicking mouse wheel + moving up/down = Zoom In/Out

- Scrolling up/down = move view up/down

- Shift + scroll up or down = move left/right

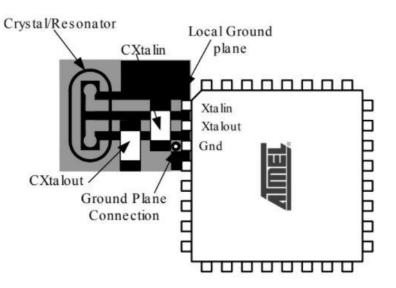

### A Bit of Theory - Clocks

#### **Important Components on the Board**

- Crystal oscillator ("clock")

- Keep the clock happy!

- Route XTAL traces close to the same length

- Provide GND shielding around clock and its supporting components

- Have clock and its supporting components close to the IC

http://ww1.microchip.com/downloads/en/DeviceDoc/Atmel-8128-Best-Practices-for-the-PCB-Layout-of-Oscillators\_ApplicationNote\_AVR186.pdf

### A Bit of Theory – Analog Components

Important Components on the Board

- Anything analog

- Analog things are sensitive to noise, so keep them away from digital signals and things that do a lot of switching

- Really just keep sensitive components away from noisy lines (protect the clock, protect analog circuits, etc.)

## A Bit of Theory

Important Components on the Board

- Components connected to differential pairs or timing-sensitive signals

- Make sure traces are close to the same length

- Plan ahead by placing the associated components near each other

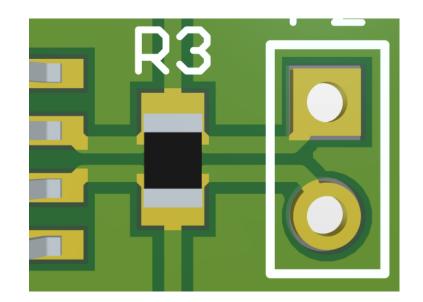

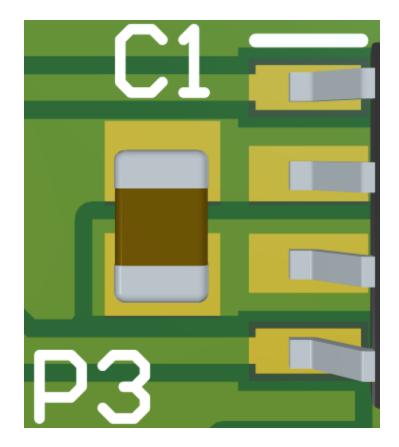

### A Bit of Theory

#### **Important Components on the Board**

- Bypass/Decoupling Capacitors

- Put them as close to the IC as possible to minimize parasitic inductance

#### **Tips and Tricks**

- Alignment Tool

- Align vertical/horizontal centers

- Align top/bottom/left/right

- Selection Filter

- Don't forget to turn it off when you're done!

## **Fine-Tuning Your Layout**

#### Tasks:

Fine-tune your layout with the tips and theory discussed in the previous slides

**Shortcuts:**

- 1 = Board Planning Mode

- 2 = 2D Mode

- 3 = 3D Mode •

- Ctrl + Scroll = Zoom ٠

- Right Click + Drag = Move schematic/PCB ٠

- Click and Hold + Space = Rotate component ٠

- Backspace = Undo Net/Trace Segment ٠

- Esc = Exit active tool ٠

- **Right click + drag from right to left = select** • entire object from part of it

- **Right click + drag from left to right = select** ٠ object that is completely covered

- Clicking mouse wheel + moving up/down = • Zoom In/Out

- Scrolling up/down = move view up/down ٠

- Shift + scroll up or down = move left/right ٠

### **Updating Rules**

- Adjusting Design Rules

- Default trace width (5 mil min, 15 mil preferred, 20 mil max)

- Differential trace width (15 mil)

- Change polygon connect style to direct connect

- Set board outline clearance so polygons stay 30 mil from edge

#### **Route the Board!**

- Route differential traces (15 mil trace width)

- Route single traces (15 mil trace width)

- Add polygons for power

- 5V polygon covering 5V pad of IC, 5V pad of bypass capacitor, and 5V pad of power header

- GND polygon across top of board

### Add (Useful) Silkscreen

- Add Tx/Rx labels to single-ended signal header

- Add L/H labels to differential pair header

- Add 5V/G labels to power header

- Add board title

- Clean everything up!

- Make sure the silkscreen is aligned and facing logical directions

#### **Adding Test Points and Mounting Holes**

- Add a test point to the GND net

- Add 4 M2 mounting holes

- Each mounting hole should be 100 mil from the edges of the corner

- M2 mounting holes have a hole size of 86.6 mil

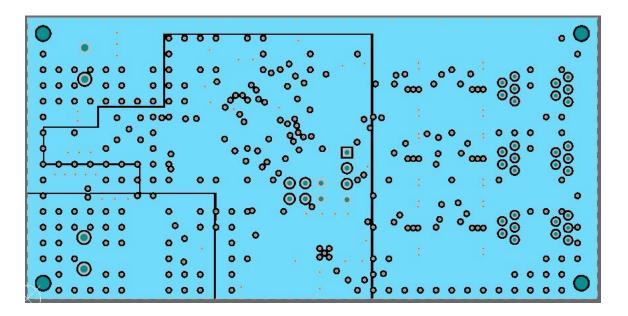

### **Preparing the Layer Stack**

#### **\*OPTIONAL\*** Tasks:

- Set up the layer stack manager so that you have four layers

- (Top, GND, Power, Bottom)

| # | Name           | Material      |   | Туре        | Weight | Thickness | Dk  | Df   |

|---|----------------|---------------|---|-------------|--------|-----------|-----|------|

|   | Top Overlay    |               |   | Overlay     |        |           |     |      |

|   | Top Solder     | Solder Resist |   | Solder Mask |        | 0.4mil    | 3.5 |      |

| 1 | Top Layer      |               |   | Signal      | 1oz    | 1.4mil    |     |      |

|   | Dielectric 2   | PP-006        |   | Prepreg     |        | 2.8mil    | 4.1 | 0.02 |

| 2 | GND            | CF-004        |   | Signal      | 1oz    | 1.378mil  |     |      |

|   | Dielectric 1   | FR-4          | 0 | Dielectric  |        | 12.6mil   | 4.8 |      |

| 3 | Power          | CF-004        | 0 | Signal      | 1oz    | 1.378mil  |     |      |

|   | Dielectric 3   | PP-006        |   | Prepreg     |        | 2.8mil    | 4.1 | 0.02 |

| 4 | Bottom Layer   |               | 0 | Signal      | 1oz    | 1.4mil    |     |      |

|   | Bottom Solder  | Solder Resist |   | Solder Mask |        | 0.4mil    | 3.5 |      |

|   | Bottom Overlay |               |   | Overlay     |        |           |     |      |

### **Preparing the Layers**

#### **\*OPTIONAL\*** Tasks:

- Pour a GND polygon across the power layer

- Pour a 5V polygon on the power layer

#### **Use Vias!**

#### **\*OPTIONAL\*** Tasks:

- Try to make a power polygon around one of the 5V pads and place vias in it to connect to the power layer

- Try to use a via to make a trace switch layers before connecting to another pad

- Try to make a ground pour across the top layer and a ground pour across the bottom layer. Add via stitching to the GND net.

### **Congratulations!**

You Now Know How To:

- Make a new PCB file

- Lay out components

- Route components using single-ended and differential traces

- Use polygons and vias

- Adjust the layer stack for multilayer boards

If you ever have questions about Altium, feel free to reach out at emarshall33@gatech.edu!